Conference Paper

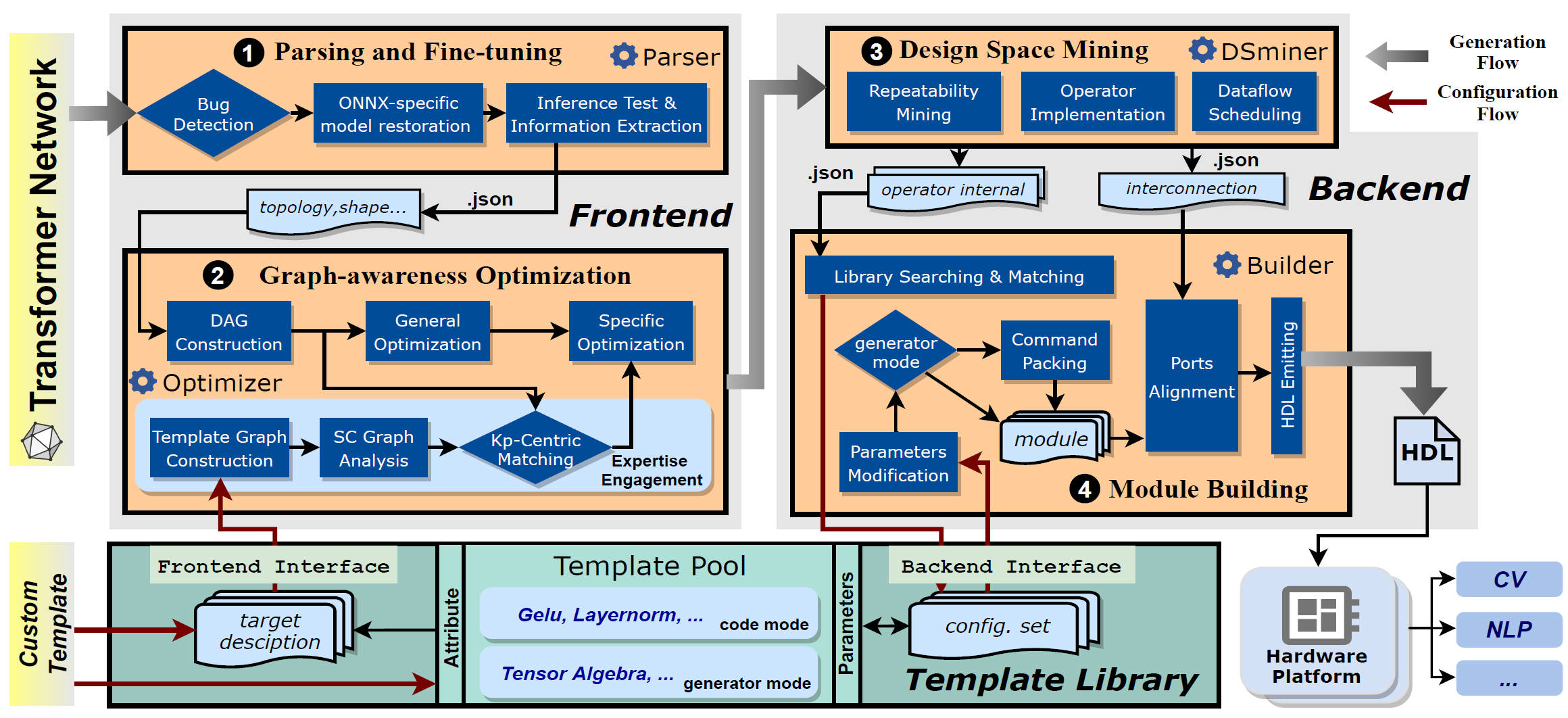

- TransLib: An Extensible Graph-Aware Library Framework for Automated Generation of Transformer Operators on FPGA

Yang Liu, Tianchen Wang, Yuxuan Dong, Zexu Zhang, Shun Li, Jun Yu, Kun Wang

2024 ACM/IEEE International Conference on Computer-Aided Design (ICCAD2024)

New Jersey, USA, October 2024.

-

Deploying Diffusion Models with Latency-Oriented Scheduling and Memory Overflow Prevention Based on Graph Optimization

Hao Zhou, Yang Liu, Hongji Wang, Enhao Tang, Shun Li, Yifan Zhang, Guohao Dai et al.

30th Asia and South Pacific Design Automation Conference (ASP-DAC2025)

Tokyo Odaiba Miraikan, Japan, January 2025. -

Fitop-Trans: Maximizing Transformer Pipeline Efficiency through Fixed-Length Token Pruning on FPGA

Kejia Shi*, Manting Zhang*, Keqing Zhao, Xiaoxing Wu, Yang Liu, Jun Yu, Kun Wang

34th International Conference on Field-Programmable Logic and Applications (FPL2024)

Turin, Italy, September 2024. -

SDAcc: A Stable Diffusion Accelerator on FPGA via Software-Hardware Co-Design [Link]

Hao Zhou, Yang Liu, Hongji Wang, Enhao Tang, Shun Li, Yifan Zhang, Kun Wang

32nd IEEE International Symposium On Field-Programmable Custom Computing Machines (FCCM2024)

Orlando, FL, USA, May 2024. -

CSTrans-OPU: An FPGA-based Overlay Processor with Full Compilation for Transformer Networks via Sparsity Exploration

Yueyin Bai*, Keqing Zhao*, Yang Liu, Hongji Wang, Hao Zhou, Xiaoxing Wu, Jun Yu, Kun Wang

61st ACM/IEEE Design Automation Conference (DAC’61)

Moscone West, San Francisco, USA, June 2024. -

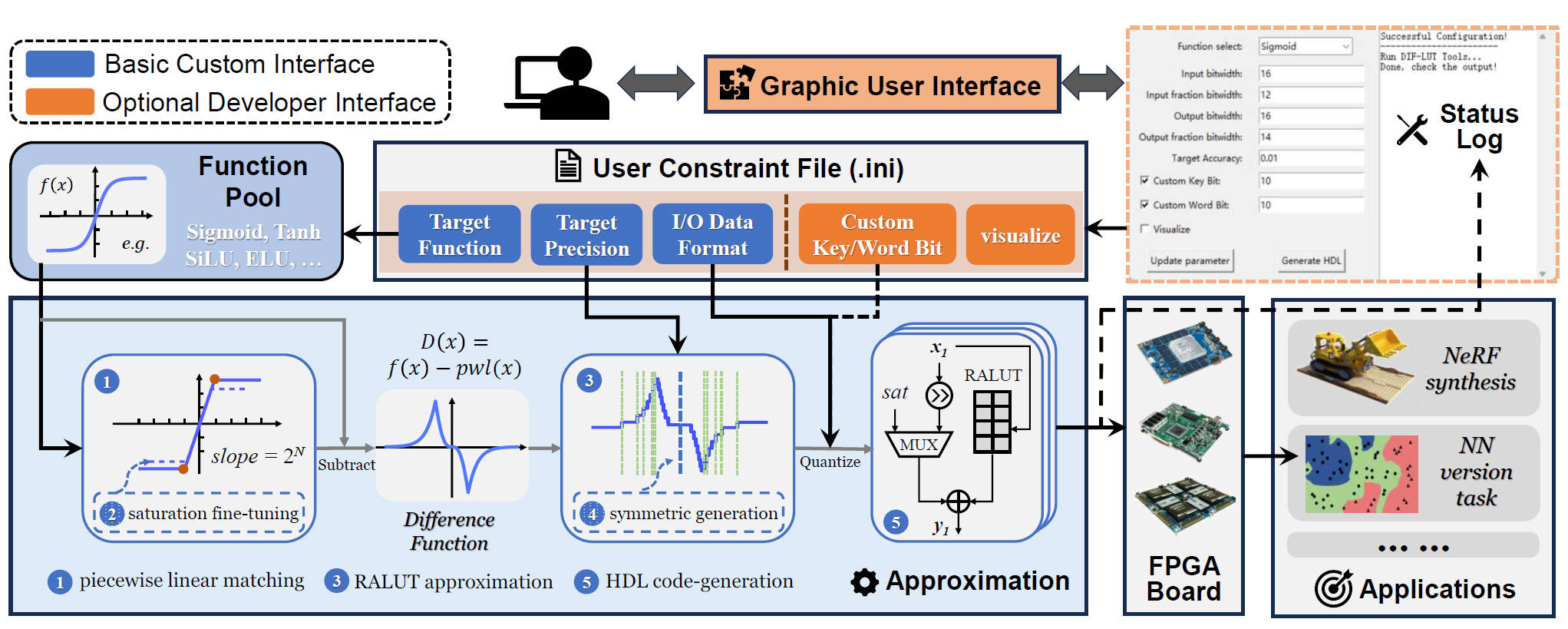

DIF-LUT: A Simple Yet Scalable Approximation for Non-linear Activation Function on FPGA [Link]

Yang Liu, Xiaoming He, Jun Yu, Kun Wang

33rd International Conference on Field Programmable Logic and Applications (FPL2023)

Chalmers University of Technology, Gothenburg, Sweden, Sep. 2023.

Journal Paper

- DIF-LUT Pro: An Automated Tool for Simple yet Scalable Approximation of Nonlinear Activation on FPGA (Under Review)

Yang Liu, Shuyang Li, Yu Li, Ruiqi Chen, Shun Li, Jun Yu, Kun Wang

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)

Selected Projects

Allo [Link] | Python, C++, HLS, MLIR; Vitis, Pytest, CI

-

Explore the potential of agile design for programmable architecture with advanced programming model

-

Develop tile-based programming interface and relevant features for dataflow architecture

TransLib | Python, Verilog HDL, C++, Shell; PyTorch, ONNX, Docker, Vivado

-

Proposed an automated and extensible framework for the operator generation of transformer networks

-

Proposed an innovative graph analysis and matching algorithms, ideal for large-scale networks

-

Designed a configurable template library of various operations to explore the design space

DIF-LUT [Link]| Python, Verilog HDL, Shell; Vivado

-

Proposes a simple yet scalable and effective approximation method for Non-linear activation in Neural Networks

-

Designed an automation toolchain for table generation and evaluation

-

Integrated as an computing unit in FPGA-based accelerator for various scenarios like DNN and Nerf

SEResnet Accelerator | Verilog HDL, C++, Python, Shell; Vivado, VStudio

-

Organized the acceleration flow of hardware and software co-design with the compiler toolchain for quantization, instruction generation, .etc

-

Deployed specific operations on programmable logic resource of SOC

-

Programmed and registered C++ operations on host CPU for simulation

The Straggler - A Vertically Scrolling Shooting Game| C++; VStudio

-

Pay homage to the classic shooting game – Raiden, based on a C++ pixel engine

-

Developed various game mechanics including skill upgrades, level progression, and boss battles

-

Incorporated numerous game features, including pause-and-save, background music, and sound effects

Undergraduate Thesis

-

A Hardware Acceleration Strategy of Squeeze-and-excite Network Based on the FPAI Chip and Compiler

Yang Liu (Advisor: Jun Yu). Final Year Project (FYP).

Expect to be developed into a journal article for submission to IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD).